首页>

耗材

首页>

耗材

商家描述

包装清单

产品评价(0)

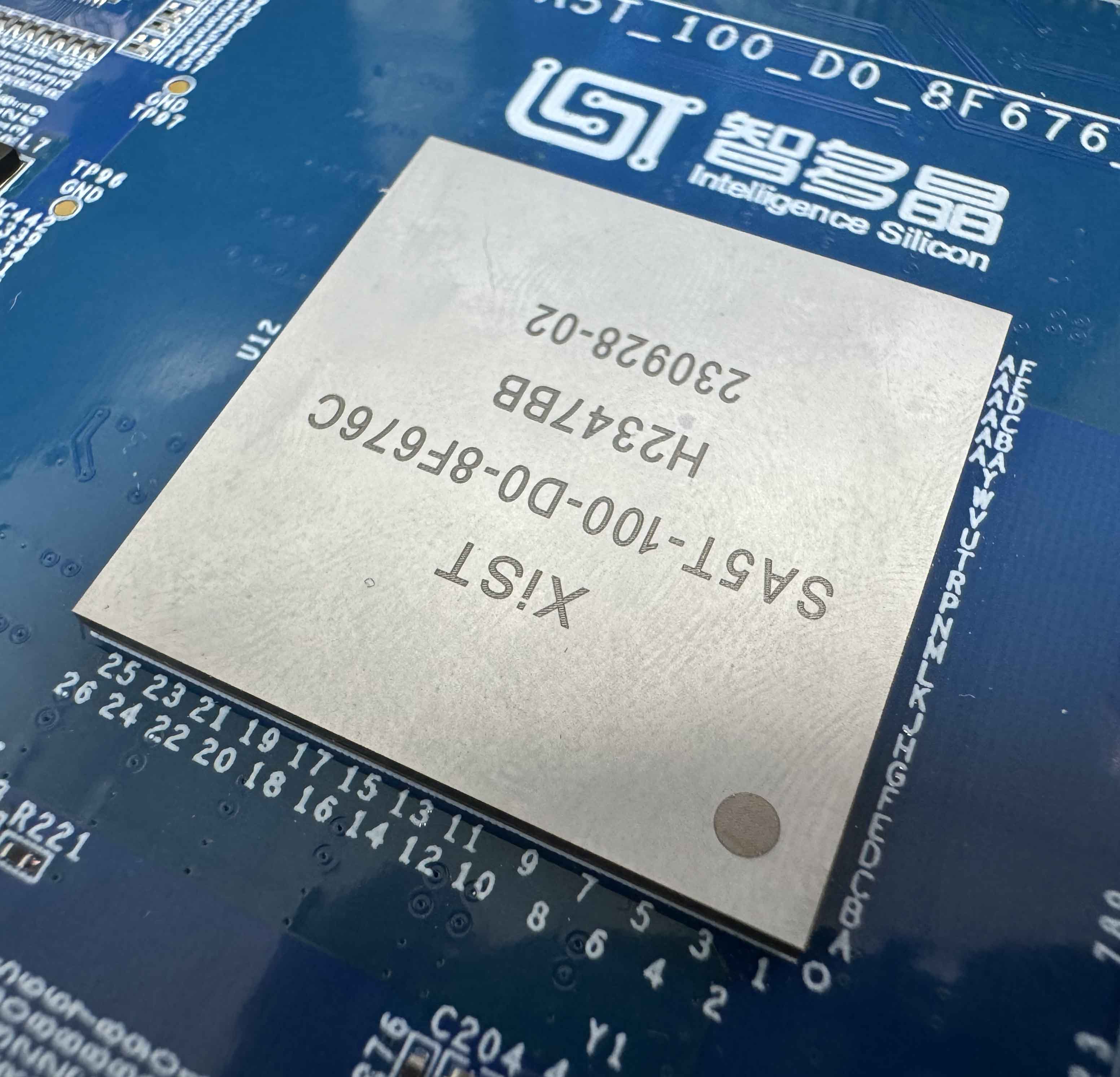

超大的逻辑资源

101,978 等效逻辑单元

多达 300 个用户 I / O

高性能可编程逻辑单元

采用 6 输入查找表(6-LUTs)

双 5-LUTs 选项

最多 128 位分布式存储器

低功耗器件

先进 28nm 高性能铜 CMOS 工艺

核电压 1.0V

嵌入式和分布式存储

Fmax = 500 MHz

嵌入块存储容量为 18Kbits, 总容量高达5,616Kbits

高达 2,040Kbit 的分布式存储

高性能,灵活的 I / O 单元

两种 IO 模块:高量程(High Range HR)和高性能(High Performance HP)

真 LVDS 接口高达 1.25 Gbps(HR)1.6 Gbps(HP)

可编程 IO 缓冲区支持多种接口:

LVCMOS3.3 / 2.5 / 1.8 / 1.5 / 1.35 / 1.2

LVTTL

PCI

BLVDS,MLVDS,RSDS,LVPECL

SSTL/DIFF-SSTL 25/18/15/135/12

HSTL/DIFF-HSTL 18/15/135

HSUL12

MIPI

施密特触发器输入,最高 0.5V 迟滞

I/O 支持热插拔

片内可调差分阻抗(OCT)

可编程上拉或下拉模式

源同步 I / O 接口

支持 7:1 Video 接口, 最高 1.6 Gbps

通用 DDRX1/X2/X4/X5 最高 1.6 Gbps

单 端 / 差 分 DQS 支 持 的 DDR1/2/3 LPDDR1/2/3 内存

增强的乘法器块

Fmax = 500 MHz

内置多个9x9/18x18/25x18具备预加法的串行乘法器, 算数逻辑单元(ALU),两层叠加实现 DSP 处理密集型应用

灵活的片内时钟

最多 32 个全局时钟

高达 24 个延时锁相环(DLL)用于高速 I/O接口

高达 7 个内置通用 PLL、提供倍频、分频、相位转移、展频等系统时钟

精度为±5%的片上振荡器

配置模式

JTAG, 从模式(PS), 主模式(AS)

配置过程支持 SED/SEC 单/多比特流检测及单比特纠正

配置过程支持多个比特流加载,可在第一个程序文件加载失败后,自动跳到 Golden 区域加载第二个程序文件

局部重配置(Partial Re-configuration)

安全

支持 AES 比特流加密及解密, 256 比特加密及解密钥匙

片上 SPI,I2C,定时器/计数器功能

兼容 IEEE1149.1:如边界扫描(BSCAN)

符合 IEEE 1532 的系统内编程

集成高速串行接口(SerDes)

集成 2 个 4 通道高速 SerDes

数据速率 6.6 /10.3 Gbps

上电顺序

先核电压(Vcc)后,再上 Vccio/Vccaux

嵌入式硬核

集成 2 个独立的 ADC(8 通道)

DDR2,3 控制器

广泛的封装选项

低成本焊线封装芯片

先进的无铅封装

101,978 等效逻辑单元

多达 300 个用户 I / O

高性能可编程逻辑单元

采用 6 输入查找表(6-LUTs)

双 5-LUTs 选项

最多 128 位分布式存储器

低功耗器件

先进 28nm 高性能铜 CMOS 工艺

核电压 1.0V

嵌入式和分布式存储

Fmax = 500 MHz

嵌入块存储容量为 18Kbits, 总容量高达5,616Kbits

高达 2,040Kbit 的分布式存储

高性能,灵活的 I / O 单元

两种 IO 模块:高量程(High Range HR)和高性能(High Performance HP)

真 LVDS 接口高达 1.25 Gbps(HR)1.6 Gbps(HP)

可编程 IO 缓冲区支持多种接口:

LVCMOS3.3 / 2.5 / 1.8 / 1.5 / 1.35 / 1.2

LVTTL

PCI

BLVDS,MLVDS,RSDS,LVPECL

SSTL/DIFF-SSTL 25/18/15/135/12

HSTL/DIFF-HSTL 18/15/135

HSUL12

MIPI

施密特触发器输入,最高 0.5V 迟滞

I/O 支持热插拔

片内可调差分阻抗(OCT)

可编程上拉或下拉模式

源同步 I / O 接口

支持 7:1 Video 接口, 最高 1.6 Gbps

通用 DDRX1/X2/X4/X5 最高 1.6 Gbps

单 端 / 差 分 DQS 支 持 的 DDR1/2/3 LPDDR1/2/3 内存

增强的乘法器块

Fmax = 500 MHz

内置多个9x9/18x18/25x18具备预加法的串行乘法器, 算数逻辑单元(ALU),两层叠加实现 DSP 处理密集型应用

灵活的片内时钟

最多 32 个全局时钟

高达 24 个延时锁相环(DLL)用于高速 I/O接口

高达 7 个内置通用 PLL、提供倍频、分频、相位转移、展频等系统时钟

精度为±5%的片上振荡器

配置模式

JTAG, 从模式(PS), 主模式(AS)

配置过程支持 SED/SEC 单/多比特流检测及单比特纠正

配置过程支持多个比特流加载,可在第一个程序文件加载失败后,自动跳到 Golden 区域加载第二个程序文件

局部重配置(Partial Re-configuration)

安全

支持 AES 比特流加密及解密, 256 比特加密及解密钥匙

片上 SPI,I2C,定时器/计数器功能

兼容 IEEE1149.1:如边界扫描(BSCAN)

符合 IEEE 1532 的系统内编程

集成高速串行接口(SerDes)

集成 2 个 4 通道高速 SerDes

数据速率 6.6 /10.3 Gbps

上电顺序

先核电压(Vcc)后,再上 Vccio/Vccaux

嵌入式硬核

集成 2 个独立的 ADC(8 通道)

DDR2,3 控制器

广泛的封装选项

低成本焊线封装芯片

先进的无铅封装

会员登录

会员登录.getTime()%>)

购物车()

购物车()

成功收藏产品

成功收藏产品